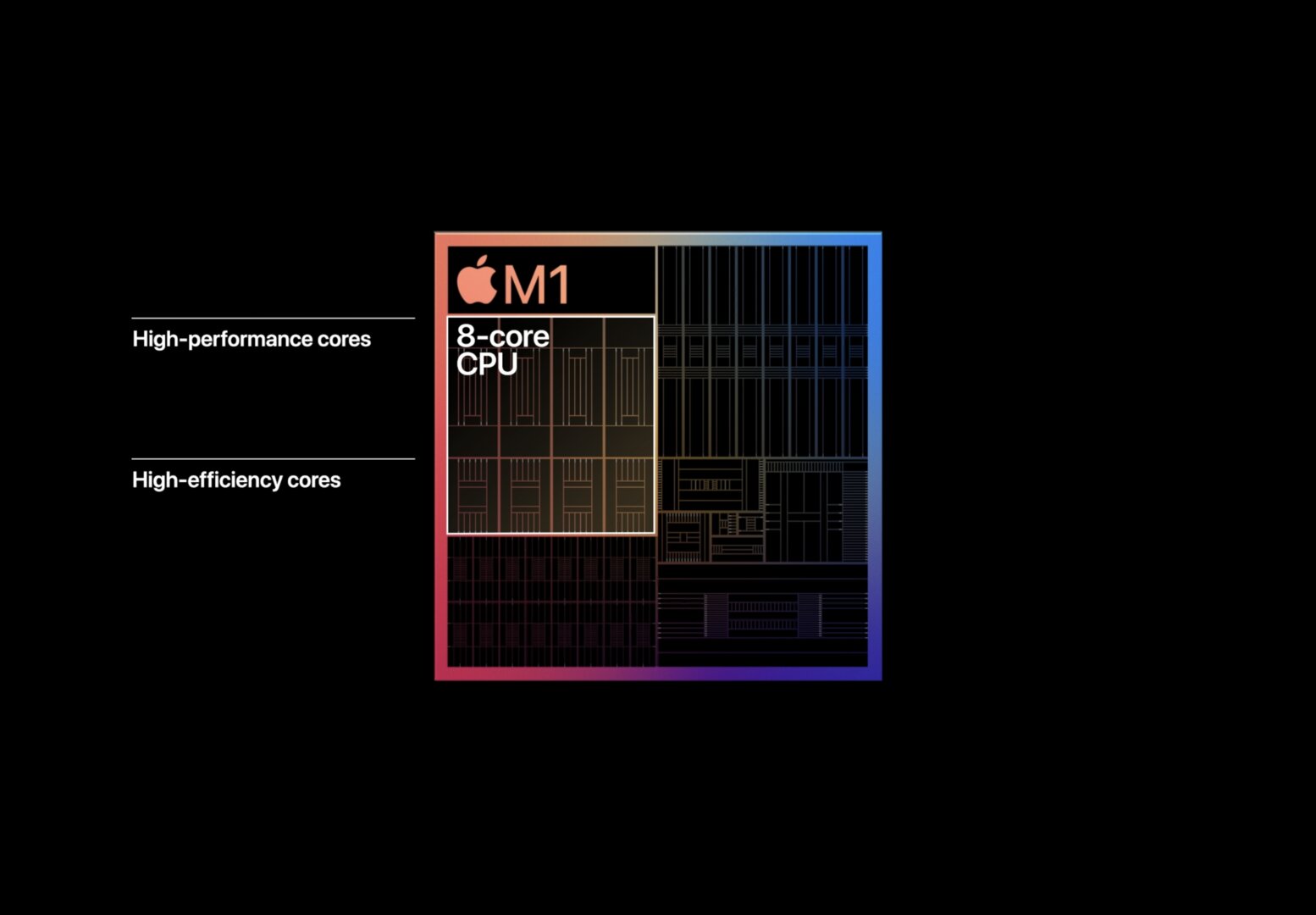

M1 ist mit 16 Milliarden Transistoren(das entspricht fast 4 CCDs mit je 8 Kernen Zen 3) in 5 nm extrem teuer in der Produktion, war wahrscheinlich teurer in der Entwicklung und wird wahrscheinlich nur in den geringen Stückzahlen produziert, denn Apples Zielsetzung ist vor allem Exklusivität. In Apples Ökosystem ist der Vorteil gegenüber den Vorgängern auf Basis älterer Intelarchitekturen riesig, vor allem bei der Energieffizienz. Aber das war es offenbar auch schon.

Wer Applepreise zahlen will, der bekommt ein sehr gutes Produkt, muss dafür aber eben auch Applepreise zahlen. Der Markt für normalpreisige Rechner bleibt davon unberührt.

Interessanter könnten die Auswirkungen von ARM bei Rechnern mit sehr vielen Kernen werden. AMDs Epic-CPUs könnten unter Druck geraten.

Zen 2 hatte 40 MB Cache je CCD und brauchte dafür etwa 40 mm², bei Zen 3 dürfte dies unveränert sein. Der Nicht-Cache mache bei Zen2 etwa 34 mm je CCD aus, bei Zen3 ist es mit etwa 41 mm² etwa 20% mehr. Angenommen der Schritt zu Zen4 fällt genauso aus, dann wären es 40 mm² für eine unveränderte Cachegröße und 49 mm² für den Rest, also 89 mm bei unveränderter Fertigung und 40/1,3+49/1,8 = 58 mm² in 5 nm. Bei weiterhin 8 Kernen je CCD ergäben 12 solcher CCDs 96 Kerne je CPU.

Zitieren

Zitieren